1、 文档目标

在AD规则里设置丝印到阻焊的间距,解决设计中丝印盖到阻焊时运行DRC不会报错的问题,并分析丝印重叠对阻焊的影响

2、 问题场景

丝印距离焊盘间距比阻焊开窗小(丝印盖到或者重贴到阻焊层),有的PCB板会报错提示修改,但是有的PCB板子却没有提示(如图1),导致打板时出现丝印缺失的情况。

丝印重叠阻焊的影响有两种:

第一个是JNH官网在PCB板打样的时候,一般是以阻焊层优先,假设丝印和焊盘重叠了,那么就会优先选择焊盘,那么附在焊盘上的丝印就会被消除掉;

第二个就是丝印附在焊盘上会影响后期的焊接,焊盘表面上会被盖上油墨,有绝缘作用,会影响上锡。

图 1

3、软硬件环境

1)、软件版本:Altium Designer 24.5.2

2)、电脑环境:Windows 11

3)、外设硬件:无

4、解决方法

1)、菜单栏打开【设计】->【规则】选项,或者使用软件默认的快捷键“DR”,打开PCB规则及约束编辑器页面框(如图2

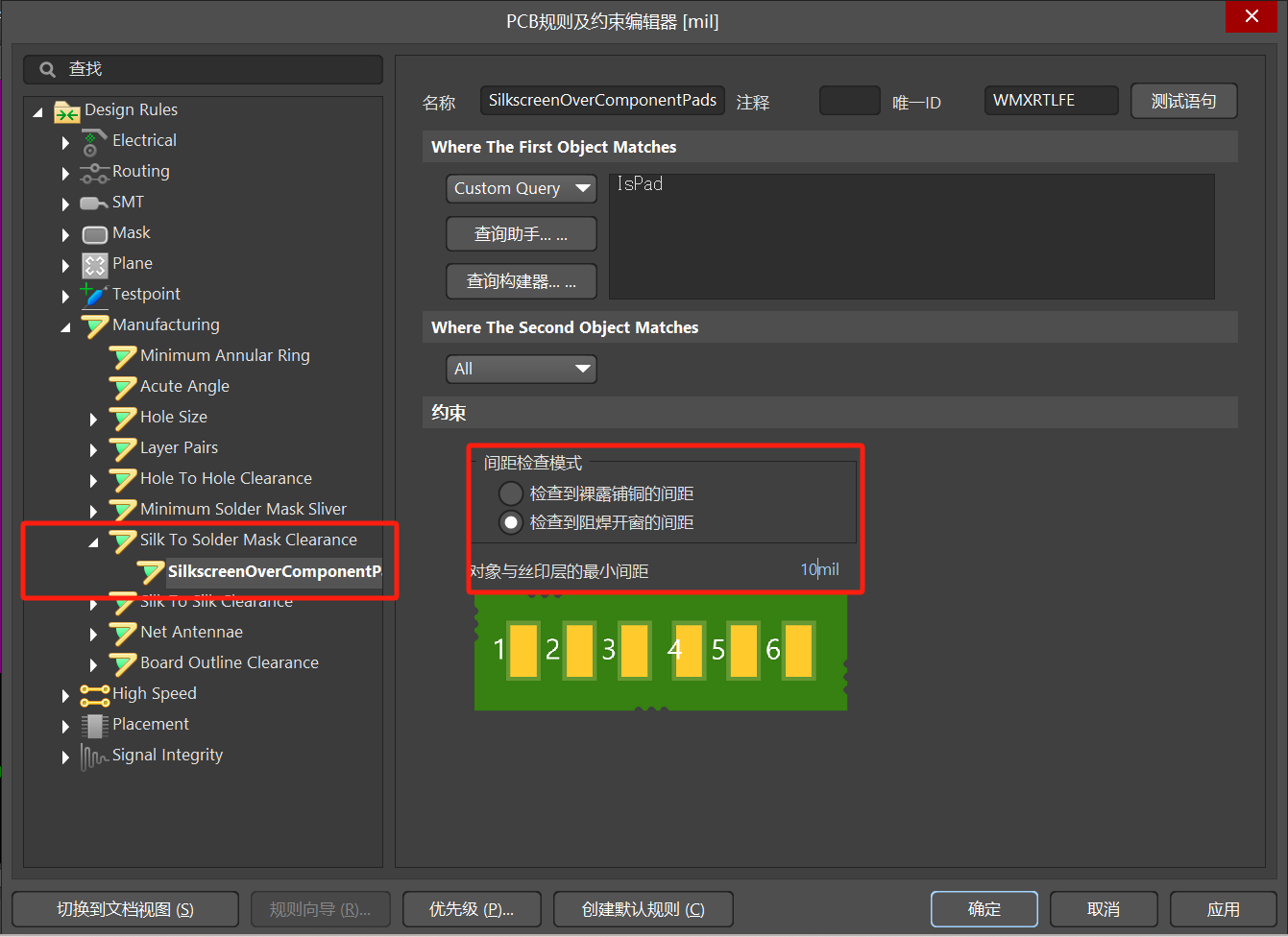

2)、在对应的对话框中找到【Manufacturing】展开点击【Silk To Solder Mask Clearance】规则,对话框右部会弹出对应的规则参数设置,设置间距检查模式为:检查到阻焊开窗的间距,然后修改项目对应的间距大小,点击应用(如图2)。

图2

3)参数设置完成后点击运行DRC可以看到,如果丝印距离阻焊比较近的或者重叠到阻焊上的丝印就会有错误提示及错误报告文档,点击报告文档即可跳转到相关报错上,

Silk To Solder Mask Clearance Constraint: (Collision < 0mil) Between Pad DS3-2(306.102mil,951.772mil) on TopLayer And Text "R13" (303.15mil,856.299mil) on TopOverlay [TopOverlay] to [TopSolder] clearance [0mil]

报错提示当前字符R13距离阻焊为0mil,小于规则设定的10mil,然后就可以根据报错信息修改PCB了(如图3)

图 3

首页 > 资源中心 > FAQ

首页 > 资源中心 > FAQ