1、 文档目标

在高速数字电路设计领域,信号时序同步是保障系统稳定运行的关键要素。针对多路并行信号传输路径的等长线设计,本文档系统阐述Altium Designer 的等长线设置方法,通过参数化控制与规则驱动策略,实现微米级精度的线长调节,为信号完整性(SI)优化提供技术支撑。

2、 问题场景

当进行FPGA并行总线、DDR内存通道或LVDS差分对等时序敏感电路布局时,需通过等长线设计确保信号到达时间偏差控制在±5%以内。本文档针对以下场景提供解决方案:

● 单线长精确标定

● 多网络同步匹配

● 规则驱动的批量化调节

3、软硬件环境

1)、软件版本:Altium Designer24.1.2

2)、电脑环境:Windows 10

3)、外设硬件:无

4、解决方法

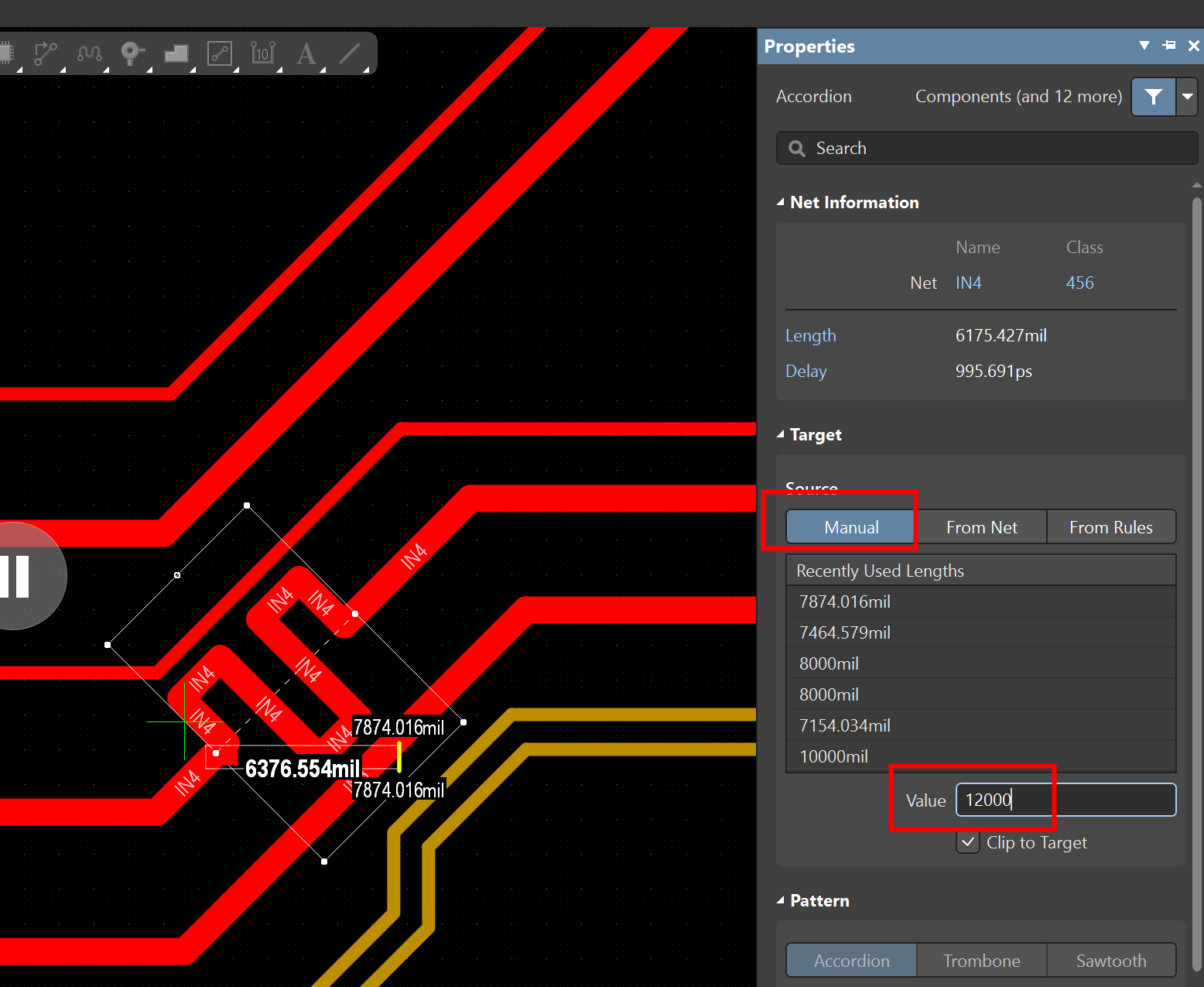

1)、使用等长调节命令后选中要调节的线,出现长度浮标,此时按下“Tab”键,打开等长线调节属性窗口。在Source处有三个选项,分别是Manual(手动输入长度),From Net(以某个网络的长度为目标),From Rules(依据设置的规则)。

图1

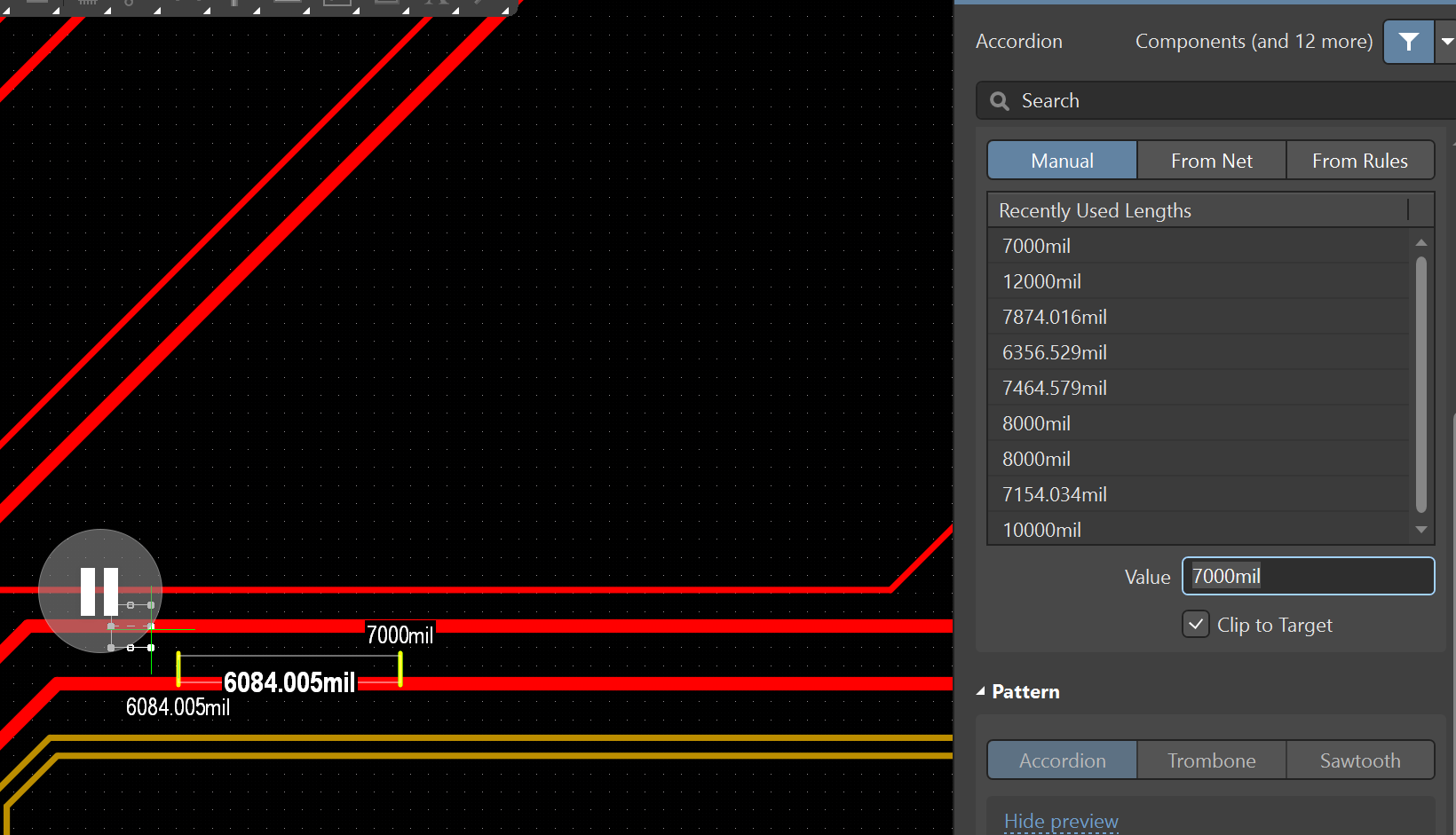

2)、在以手动输入为目标时,Recently Used Lengths栏会列出当前使用过的长度,如果需要的长度在里面,可以直接选择。如果没有需要的长度,可以在Value处手动输入需要的长度,此处手动输入7000。

图2

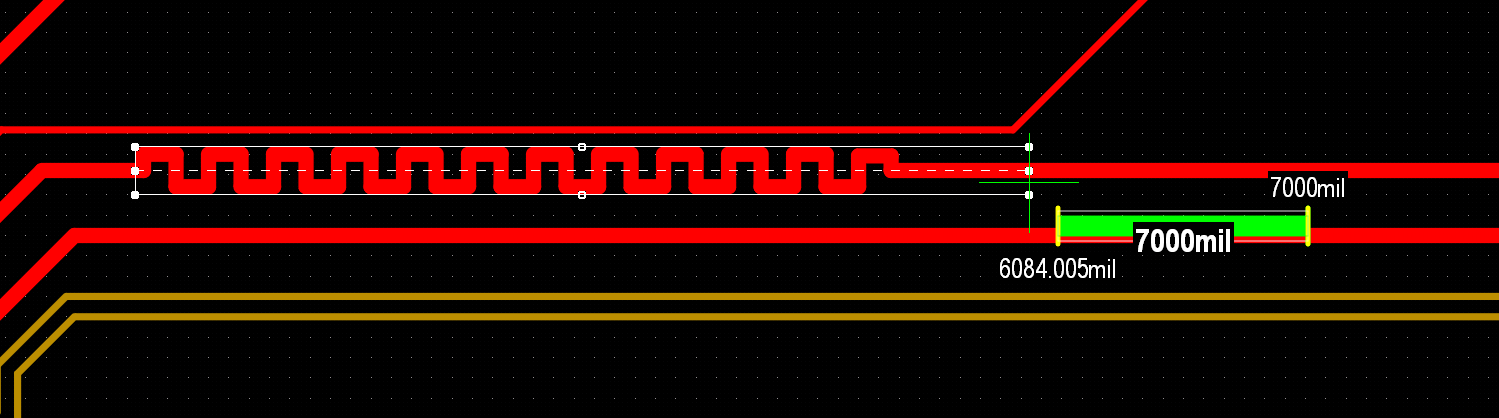

3)、此时长度浮标上数值变动,左侧为该导线原长度,右侧为目标值,目标值变更为7000,拖动等长线到目标值。

图3

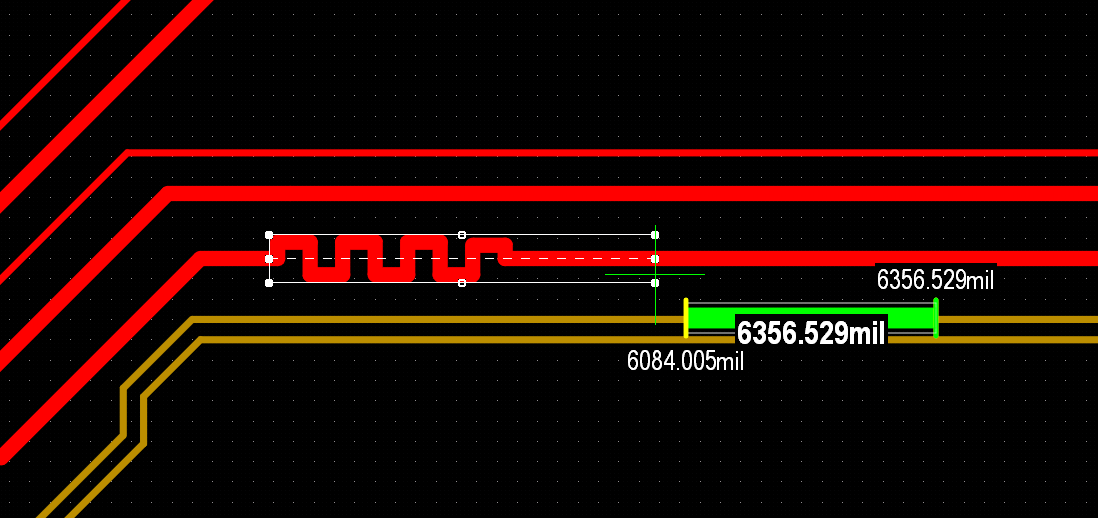

4)、当选择From Net时,会列出当前PCB上所有已布好的线以及它们的长度,选择需要遵循的目标网络,此时选择IN5,其长度为6356.529。

图 4

5)、浮标处目标值变更为6356.529,调节等长线。

图5

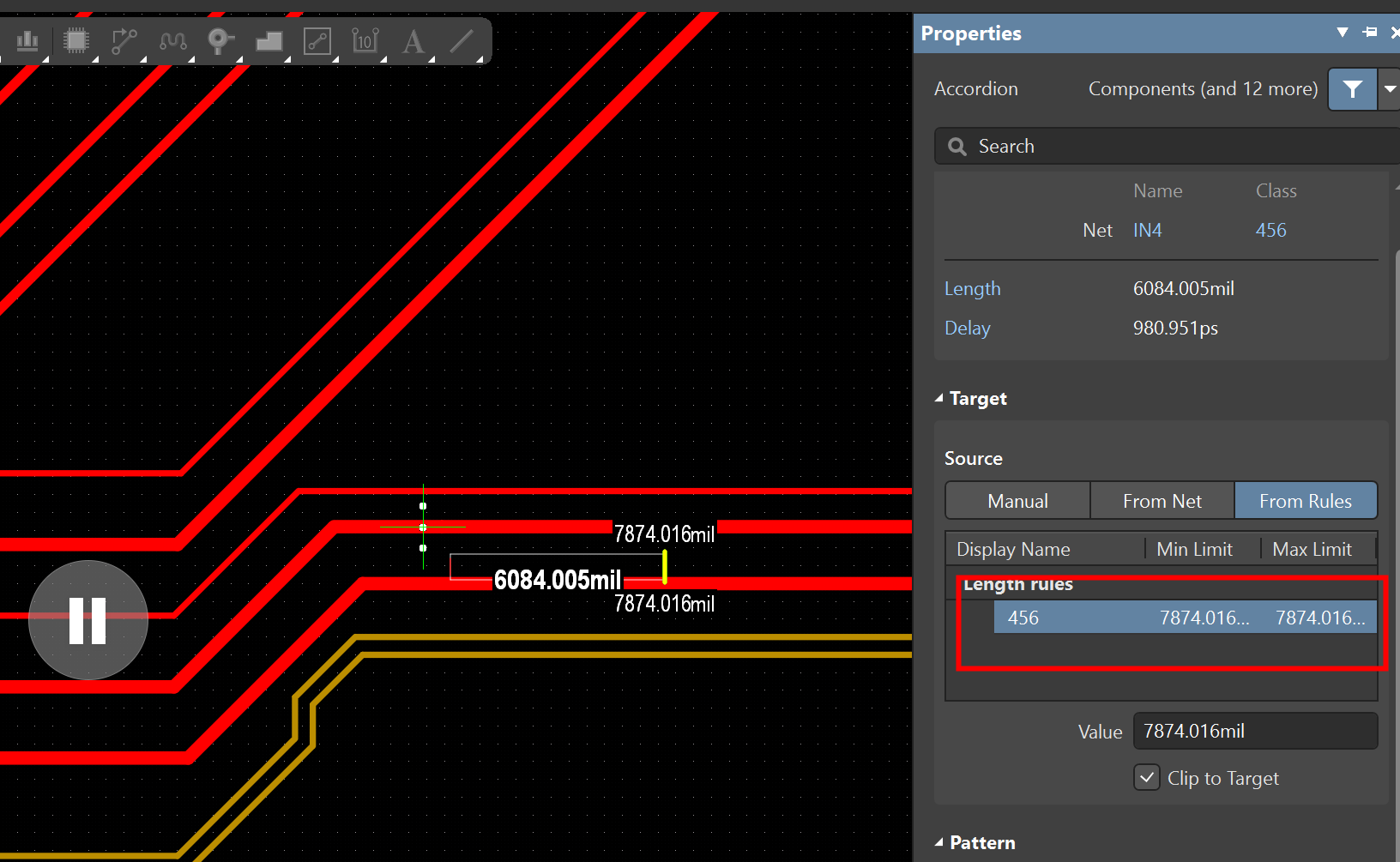

6)、选择From Rules,等长线调节的目标将遵循设置的规则,需在等长规则中以目标网络先设置一条规则。设置规则后才能在From Rules中看到长度规则,将其选中后,就能以规则设定目标进行等长线调节。

图6

5、技术价值

通过等长线功能可以精准匹配多个网络的信号传输路径线长,精确控制信号偏差在合理范围,保证信号的完整性。

首页 > 资源中心 > FAQ

首页 > 资源中心 > FAQ